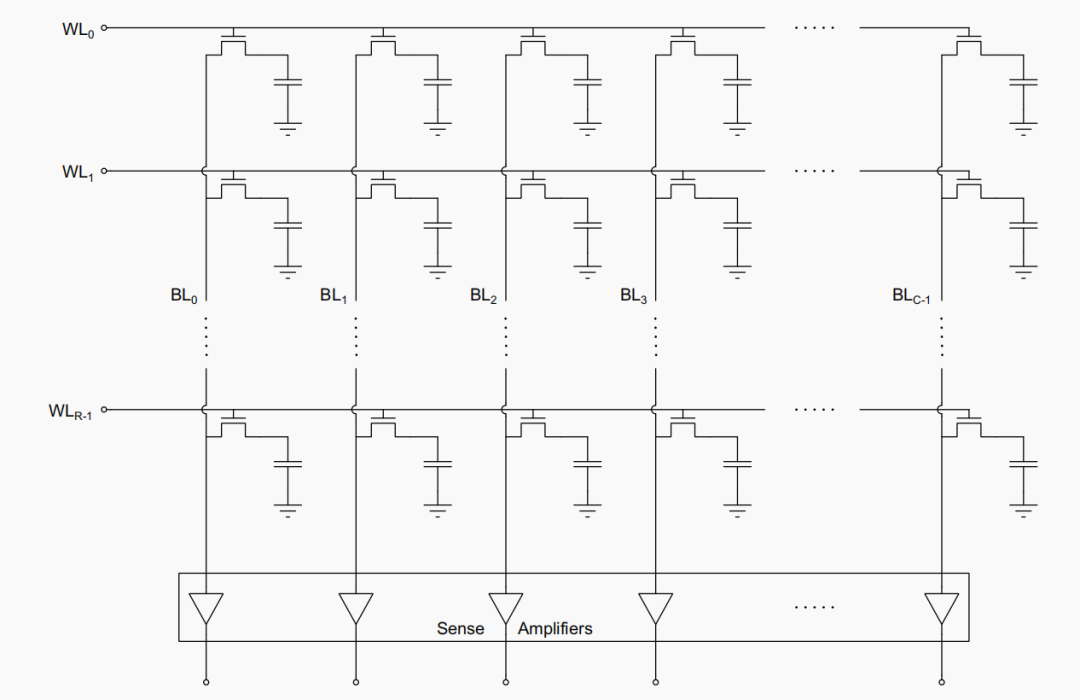

首要,DRAM一般被组织成一个矩形的存储单元阵列,这些存储单元依照行和列的方法摆放。幻想一下,就像一个巨大的表格,每个单元格都是一个存储cell。下图展现了一个简化的根本DRAM cell arrays结构,其间包括R行和C列的cell。一个典型的DRAM array或许会包括数百乃至数千个这样的cell。

这些cell是怎么被拜访的呢?答案是经过行地址和列地址。行地址线(也便是咱们常说的字线)连接到nMOS晶体管的栅极,而列线则连接到活络放大器。这种规划使得咱们我们能够经过特定的行和列地址来定位并拜访任何一个DRAM cell。

但是,arrays的巨细并不是越大越好。更大的arrays虽能存储更多的信息,但它们也需求更长的字线和位线。更长的字线和位线意味着更高的电容,这会带来一些问题。首要,电容的增加会使得位线上的电压摇摆在读取时变得很细小,这使得检测变得困难。其次,更高的电容也代表着更大的arrays在操作时会更慢。

在现代DRAM中,一个典型的arrays巨细是8K字(行)乘以1024位(列)。这在某种程度上预示着每个DRAM芯片能够存储8192个数据单元,每个单元能够存储1024位数据。

你或许还听说过DRAM Banks。一个DRAM Banks一般包括4到16个DRAM arrays,这些arrays能够一起被拜访。因而,每逢内存操控器拜访DRAM时,DRAM芯片会传输或接纳与arrays数量持平的位数。每个array供给一个位到输出引脚。DRAM芯片被描绘为xN,其间N指的是内存array和输出引脚的数量。例如,一个x8 DRAM表明DRAM至少有八个内存array,这在某种程度上预示着每次内存操控器拜访DRAM时,DRAM会传输或接纳8位。

文章出处:【微信号:数字芯片实验室,微信大众号:数字芯片实验室】欢迎增加重视!文章转载请注明出处。

LDO(Low Dropout Regulator)是一种低压差线性稳压器,它可供给安稳的输出电压,一起具有较低的功耗和噪声。本文将具体的介绍LDO的

TEA1504开关电源低功耗操控IC摘要:介绍了 Philips 公司开发的 Green Chip TM 绿色芯片 TEA1504 的

电路 /

IGBT主要由四层半导体资料构成,分别是P型、N型、P型和N型。从上到下依次为:发射极、集电极、P型基区和N型基区。在P型基区和N型基区之间有一个

剖析 /

激光加工中的“零级光妖怪”,怎么智斗这位“不速之客”?——《黑神话:悟空》版

飞凌嵌入式受邀参与openEuler Embedded Meetup(广州站)